# Estimation of Time to Failure Distribution in SRAM due to Trapped Oxide Charges **Dimple Kochar and Animesh Kumar** Electrical Engineering, Indian Institute of Technology Bombay, India **2021 IEEE International Symposium on Circuits and Systems** May 22-28, 2021 Virtual & Hybrid Conference

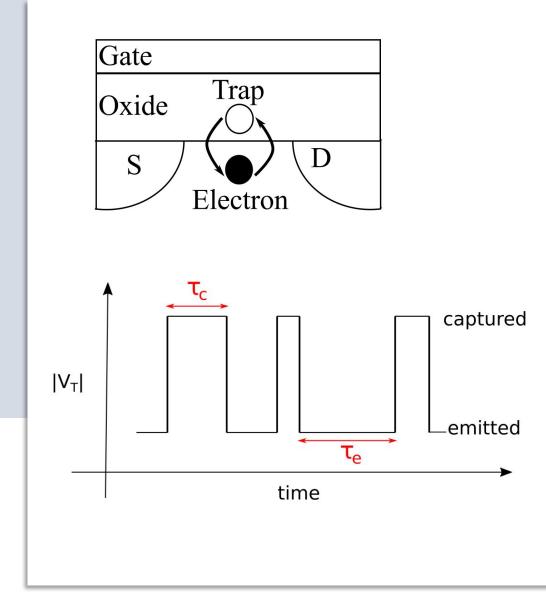

## Random Telegraphic Noise (RTN)

$$f(\tau_c) = \frac{1}{\bar{\tau}_c} e^{-\frac{\tau_c}{\bar{\tau}_c}}, \quad \tau_c \ge 0$$

$$f(\tau_e) = \frac{1}{\bar{\tau}_e} e^{-\frac{\tau_e}{\bar{\tau}_e}}, \quad \tau_e \ge 0$$

- Trap captures an electron for time:  $\tau_e$ Trap has no captured electron for time:  $\tau_e$

- $\tau_{c}$  and  $\tau_{e}$  are random variables.

- The capture and release is modeled by two Poisson processes, which occur alternately one after each other.

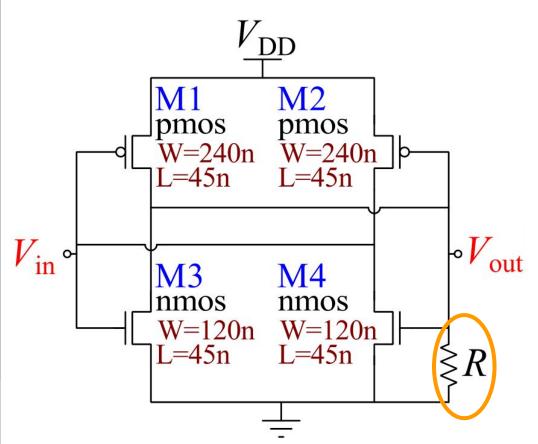

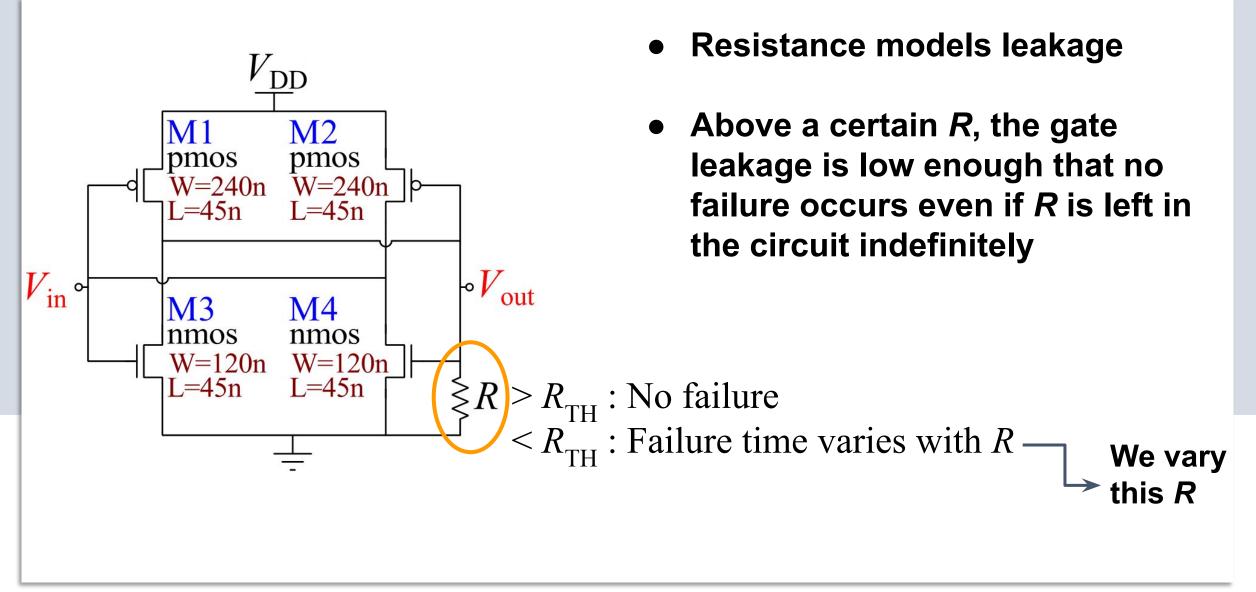

#### **RTN Model in Circuit**

- The single trap RTN phenomenon is modelled using a resistor

- The time that the resistor is a part of the circuit: captured electron in trap The time for which the resistor is removed: released electron from trap

- Both these times are modelled as Poisson processes

#### **RTN Model in Circuit**

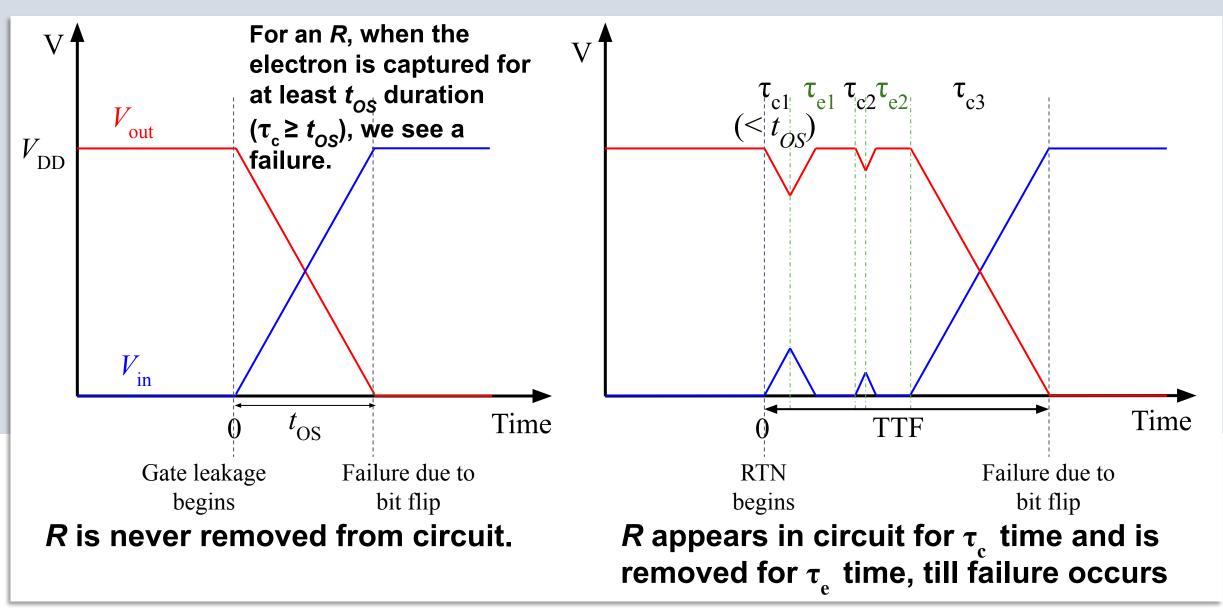

# Failure due to RTN

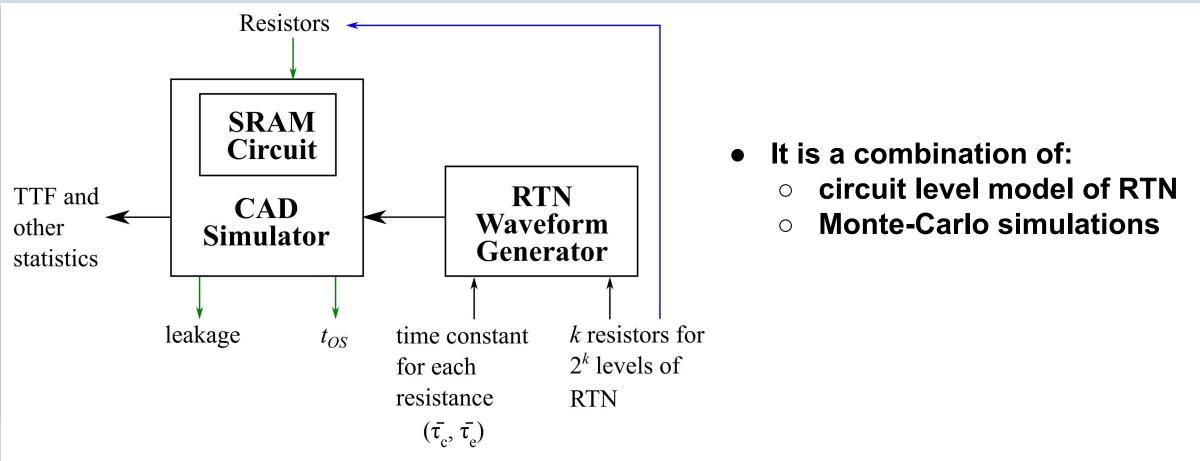

#### **Simulation Methodology**

$$f(\tau_c) = \frac{1}{\bar{\tau}_c} e^{-\frac{\tau_c}{\bar{\tau}_c}}, \quad \tau_c \ge 0$$

$$f(\tau_e) = \frac{1}{\bar{\tau}_e} e^{-\frac{\tau_e}{\bar{\tau}_e}}, \quad \tau_e \ge 0$$

•

$$\bar{\tau_c} = \bar{\tau_e} = \bar{\tau}$$

(for analytical convenience)

- Let T be the time to failure of a stored bit.

If τ̄ = 100t<sub>os</sub>, Prob(T = t<sub>os</sub>) ≈ 0.99.

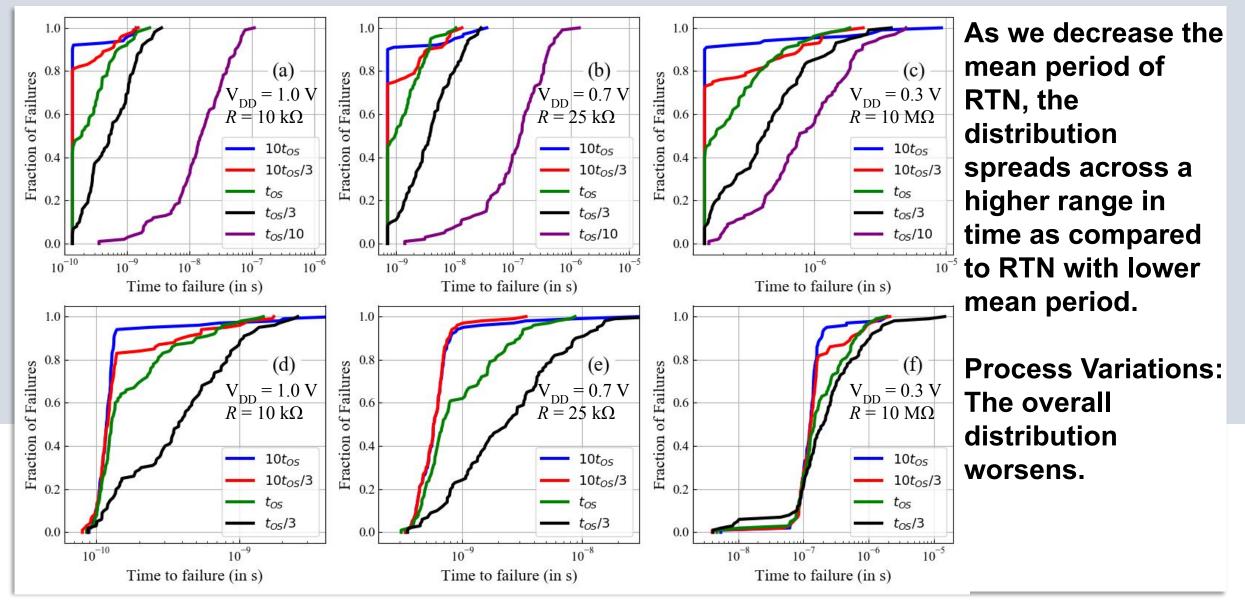

So, τ̄ is selected in the range of 0.1t<sub>os</sub> to 10t<sub>os</sub>.

- Repeated Monte-Carlo trials (stochastic simulations) are run

#### **Overview: Method to Estimate TTF Distribution**

- This approach is flexible:

- any circuit-level (or device level) model for RTN + Monte-Carlo methods = estimate the TTF distribution for any SRAM circuit.

#### **Results**

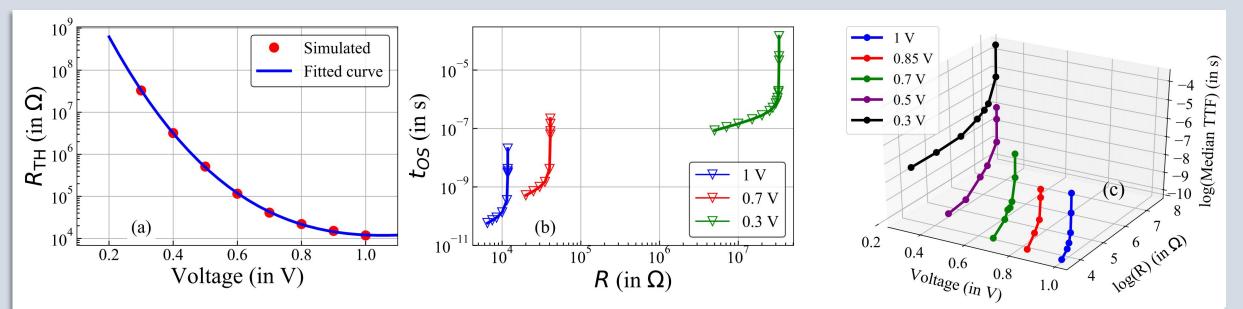

a)  $V_{DD}$  vs  $R_{TH}$ . For a  $V_{DD}$ , leakage below a certain value  $\rightarrow$  no failure due to RTN.

- b)  $t_{os}$  for different voltages has a singularity at  $R_{TH}$ .

- c) Median time to failure increases as we increase resistance or supply voltage, keeping the other fixed.

#### **Results**

## Summary

- Trapping and detrapping of charges in the oxide interface of a MOSFET leads to a random telegraphic noise (RTN) injection

- This event negatively affects the reliability of stored bit in an SRAM cell

- In this work, a method to estimate the statistical distribution of time to failure of a stored bit in an SRAM cell is proposed.

- The proposed method includes a composition of a trapping/detrapping current injection model, a Monte-Carlo simulator, and a circuit-level abstraction of an SRAM cell.

- As an example of the proposed method, using circuit-level simulations, the effect of RTN due to a single-trap model is showcased for 45 nm CMOS technology. Process variation simulations are also performed.