# 83: A 0.75mm<sup>2</sup> 407µW real-time speech audio denoiser with quantized cascaded redundant convolutional encoder-decoder for wearable IoT devices

Dimple Vijay Kochar, Maitreyi Ashok, Anantha P. Chandrakasan

Electrical Engineering and Computer Science Massachusetts Institute of Technology, Cambridge, MA

#### Outline

- Introduction

- Design Features

- Algorithm Design

- Quantization Scheme

- Top-level Chip Architecture

- 1D Convolution Dataflow

- Results

- Conclusion

#### Outline

- Introduction

- Design Features

- Algorithm Design

- Quantization Scheme

- Top-level Chip Architecture

- 1D Convolution Dataflow

- Results

- Conclusion

Growing Need for Audio Denoising in Wearable IoT Devices

Growing Need for Audio Denoising in Wearable IoT Devices

- Wearable IoT devices require effective audio denoising

- Clear communication during calls

- High-quality audio recordings

- Enhanced voice assistants

Growing Need for Audio Denoising in Wearable IoT Devices

- Wearable IoT devices require effective audio denoising

- Clear communication during calls

- High-quality audio recordings

- Enhanced voice assistants

Growing Need for Audio Denoising in Wearable IoT Devices

- Wearable IoT devices require effective audio denoising

- Clear communication during calls

- High-quality audio recordings

- Enhanced voice assistants

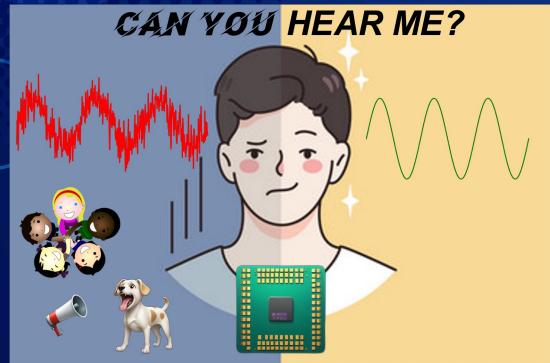

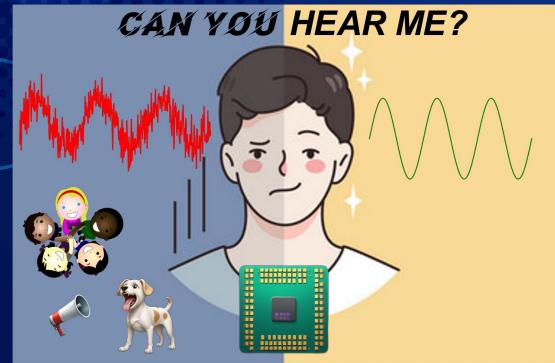

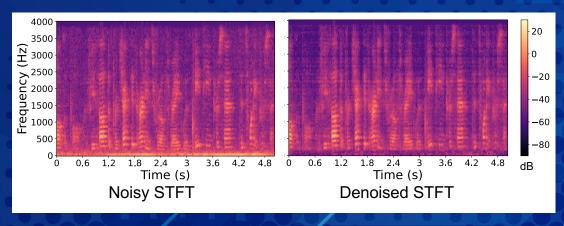

Audio denoising is a complex task involving audio reconstruction

Audio Denoising is Hard for Wearable IoT Devices

Audio Denoising is Hard for Wearable IoT Devices

- Wearables require:

- Superior audio quality

- Low power consumption

- Realtime performance

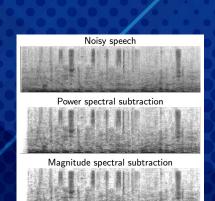

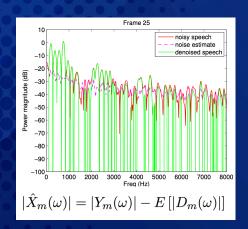

#### Audio Denoising is Hard for Wearable IoT Devices

- Classical methods are rigid noise estimation

- Fixed algorithms and parameters

- Wearables require:

- Superior audio quality

- Low power consumption

- Realtime performance

#### Audio Denoising is Hard for Wearable IoT Devices

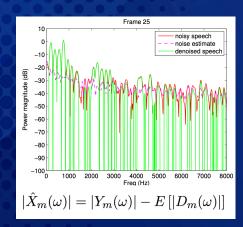

$|\hat{X}_m(\omega)|^2 = |Y_m(\omega)|^2 - E\left[|D_m(\omega)|^2\right]$

- Classical methods are rigid noise estimation

- Fixed algorithms and parameters

- Wearables require:

- Superior audio quality

- Low power consumption

- Realtime performance

- CNNs offer flexibility but demand efficiency

- Generalizable across noise types

- Finetune/retrain, downstream deploy

Past ML-Based Audio Processing

Past ML-Based Audio Processing

High Performance:

Recent deep learning algorithms excel in audio processing

Past ML-Based Audio Processing

Recent deep learning algorithms excel in audio processing

#### Challenges:

- High computational complexity

- Large model sizes

- Substantial power and resource requirements

Past ML-Based Audio Processing

Recent deep learning algorithms excel in audio processing

#### Challenges:

- Large model sizes

- Substantial power and resource requirements

#### Feasibility Issues:

Unsuitable for IoT devices due to energy and size constraints

Past ML-Based Audio Processing

Recent deep learning algorithms excel in audio processing

#### Challenges:

- High computational complexity

- Large model sizes

- Substantial power and resource requirements

- Feasibility Issues:

- Unsuitable for IoT devices due to energy and size constraints

Convolutional Encoder-Decoder (CED) models show promise in frequency-domain audio processing

Practicality depends on efficient hardware design to reduce computational demands

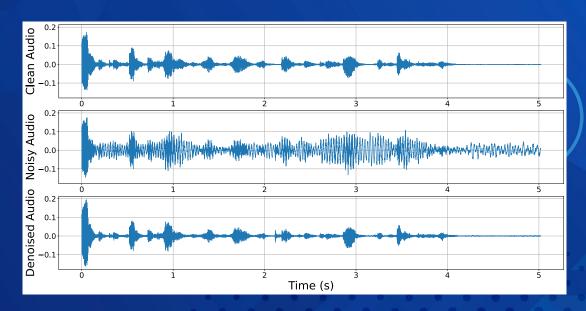

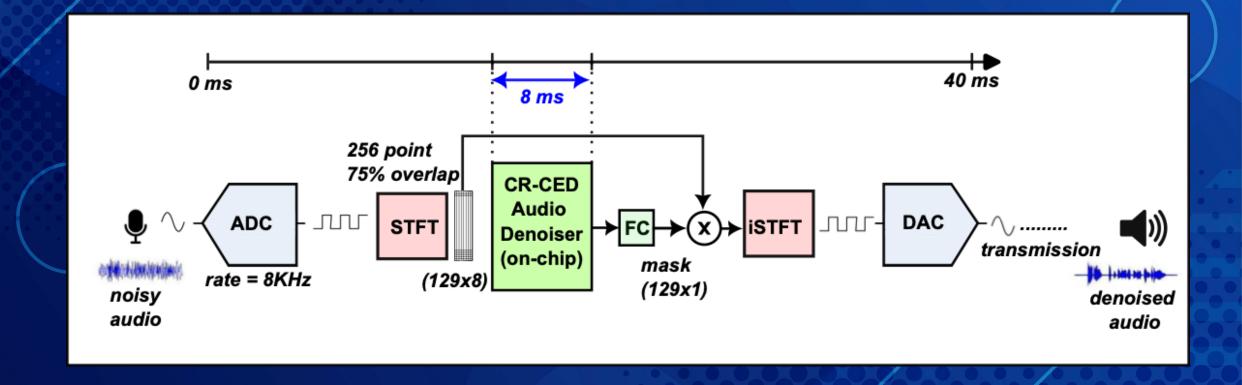

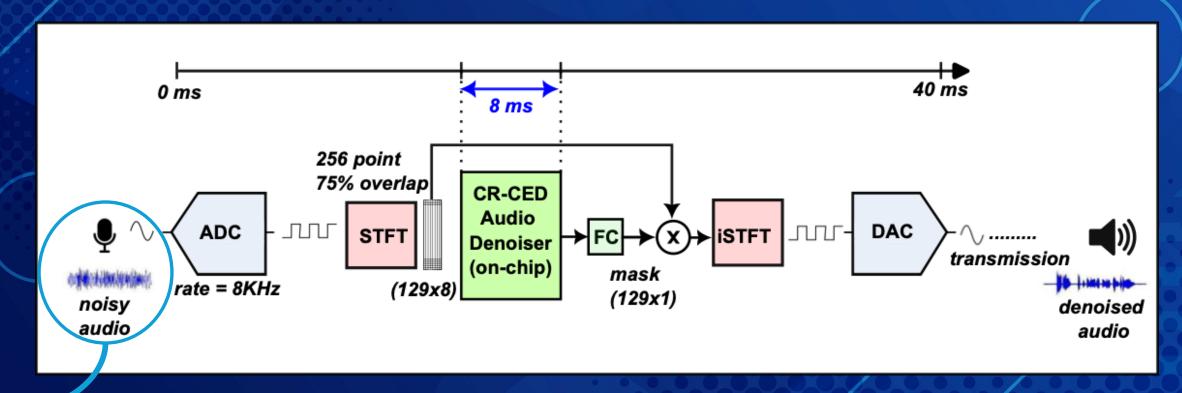

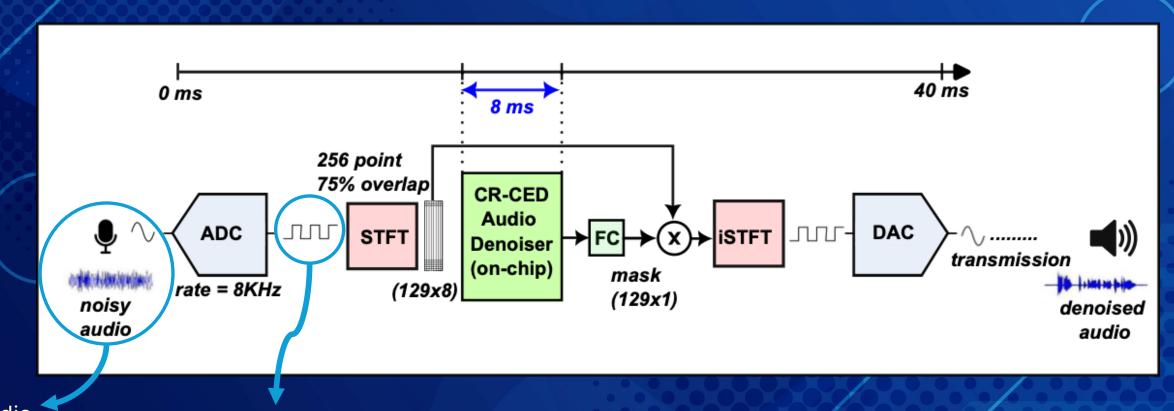

Our Solution: A Real-Time Low-Power Denoising System

Our Solution: A Real-Time Low-Power Denoising System

Our Solution: A Real-Time Low-Power Denoising System

Lower computational costs with optimized quantization

Our Solution: A Real-Time Low-Power Denoising System

Lower computational costs with optimized quantization

Low on-chip memory accesses, highest audio quality score

Our Solution: A Real-Time Low-Power Denoising System

Lower computational costs with optimized quantization

Low on-chip memory accesses, highest audio quality score

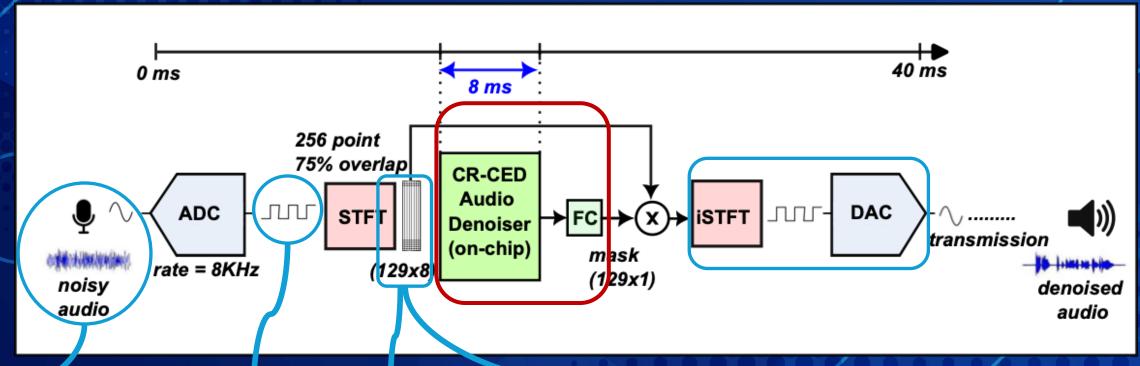

Processes audio in 8ms per frame, consumes 407µW

Our Solution: A Real-Time Low-Power Denoising System

Lower computational costs with optimized quantization

Low on-chip memory accesses, highest audio quality score

Processes audio in 8ms per frame, consumes 407µW

#### Outline

- Introduction

- Design Features

- Algorithm Design

- Quantization Scheme

- Top-level Chip Architecture

- 1D Convolution Dataflow

- Results

- Conclusion

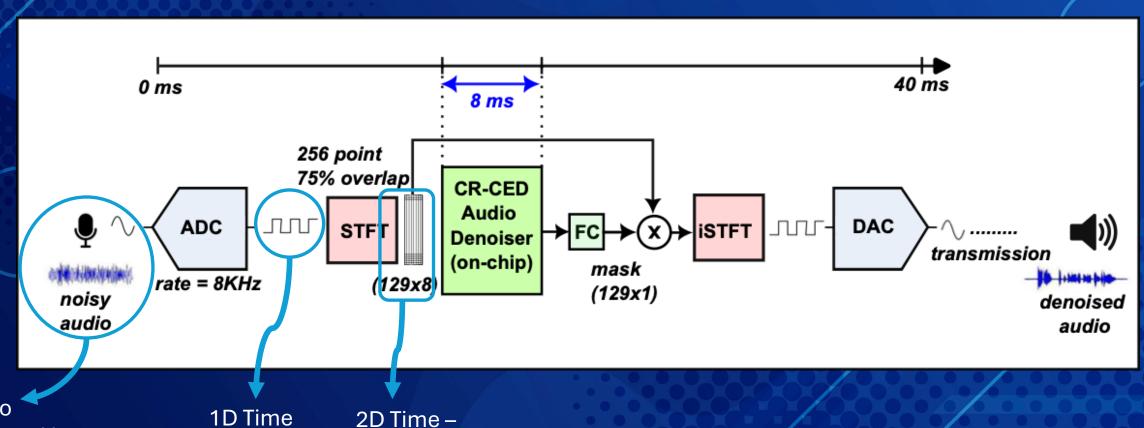

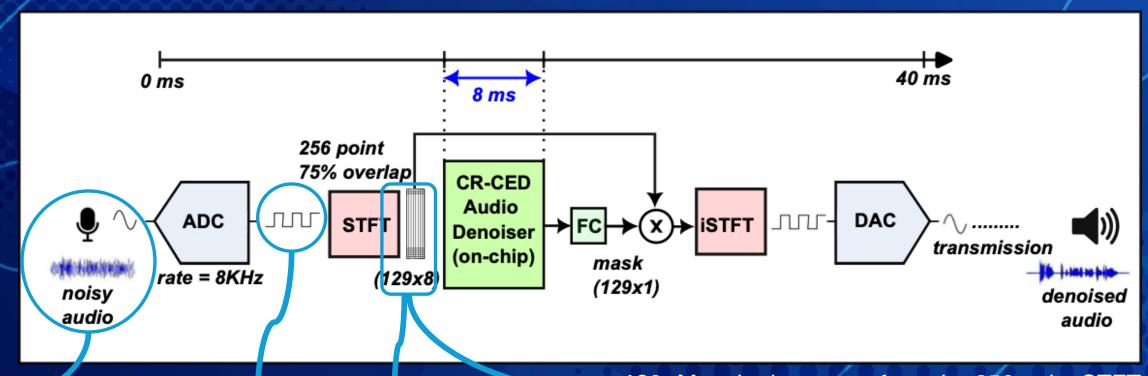

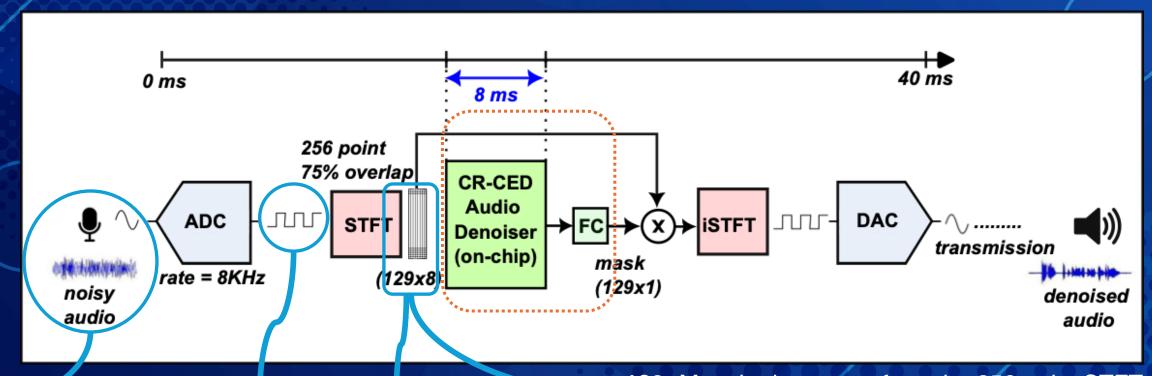

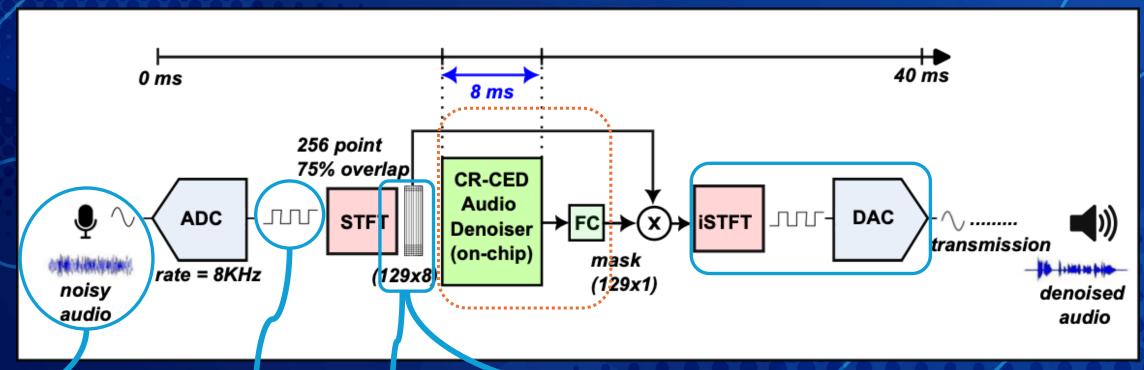

## Algorithm Design End-to-end Audio Denoiser Pipeline

**End-to-end Audio Denoiser Pipeline**

**End-to-end Audio Denoiser Pipeline**

Audio captured by microphone

**End-to-end Audio Denoiser Pipeline**

Audio captured by microphone

1D Time series

DESIGN CINEDADE System

**End-to-end Audio Denoiser Pipeline**

Audio captured by microphone

1D Tim series

2D Time – Frequency series

DESIGN Embedded System

**End-to-end Audio Denoiser Pipeline**

Audio captured by microphone

1D Time series

2D Time – Frequency series

**129:** Magnitude vectors from the 256-point STFT, 129 points retained (symmetric half of 256)

**End-to-end Audio Denoiser Pipeline**

Audio captured by microphone

1D Time series

2D Time – Frequency series **129:** Magnitude vectors from the 256-point STFT, 129 points retained (symmetric half of 256)

**End-to-end Audio Denoiser Pipeline**

Audio captured by microphone

1D Time series

2D Time – Frequency series **129:** Magnitude vectors from the 256-point STFT, 129 points retained (symmetric half of 256)

**End-to-end Audio Denoiser Pipeline**

Audio captured by microphone

1D Time series

2D Time – Frequency series **129:** Magnitude vectors from the 256-point STFT, 129 points retained (symmetric half of 256)

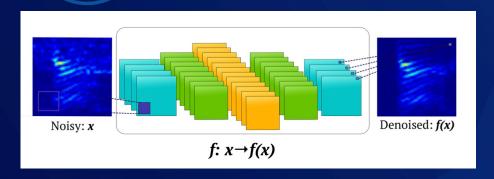

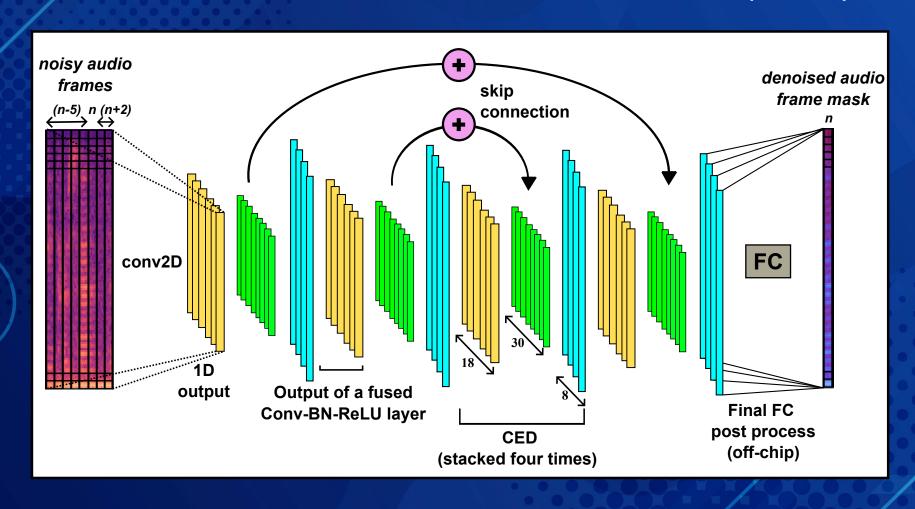

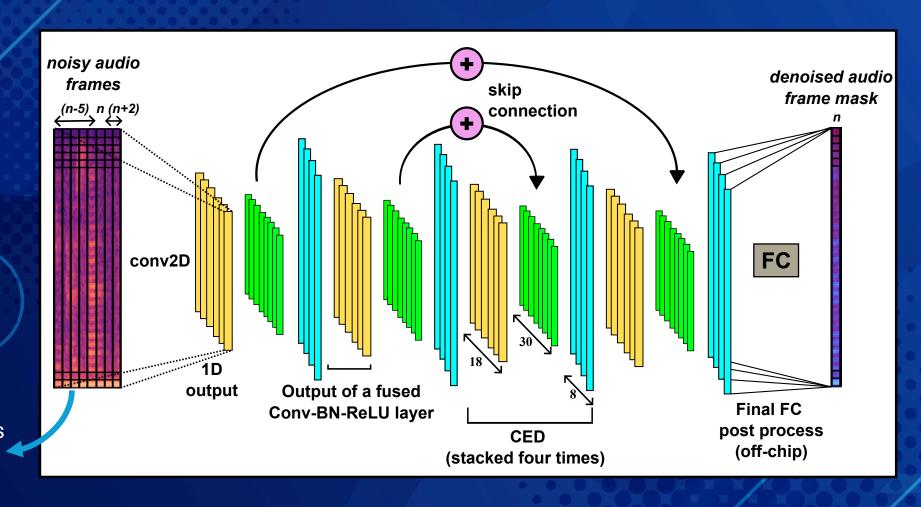

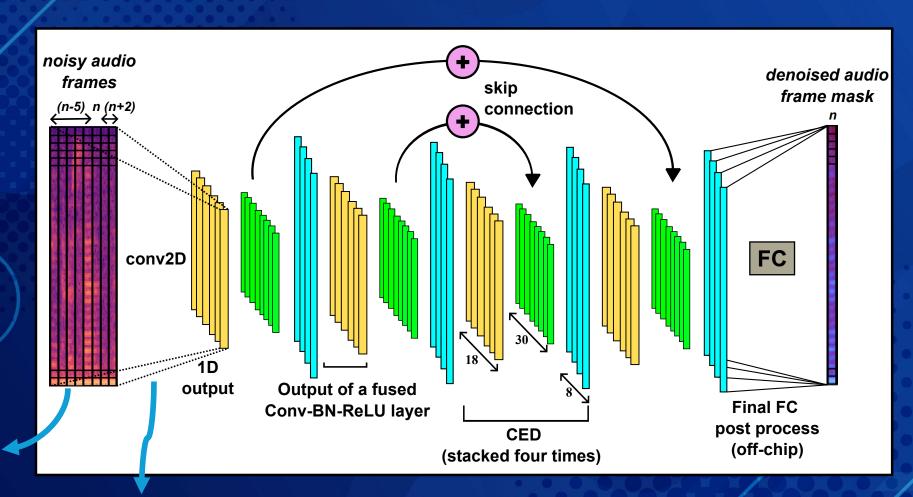

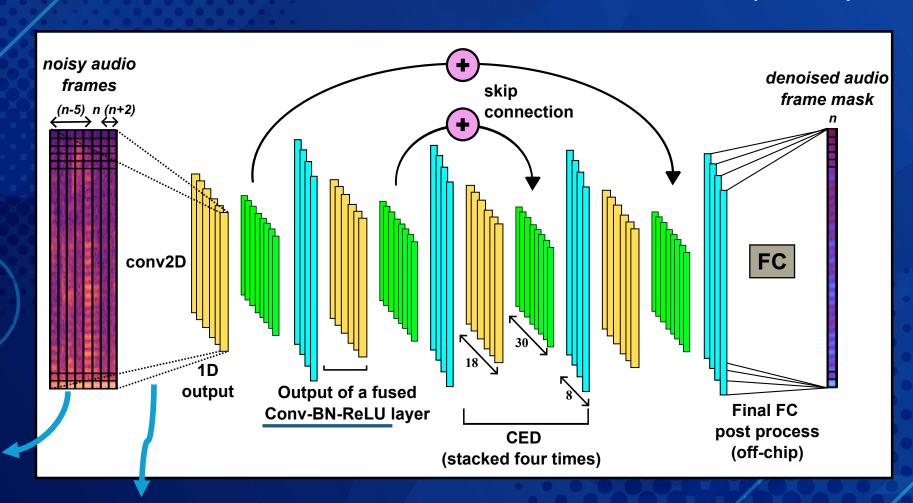

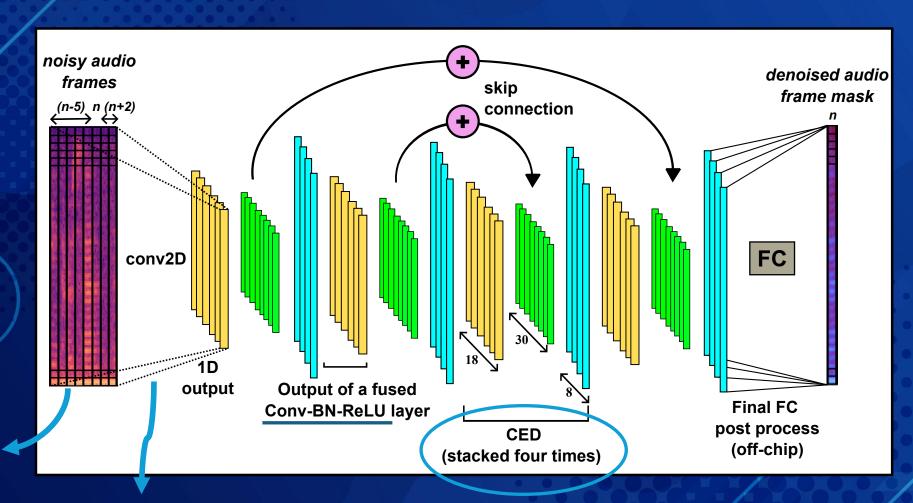

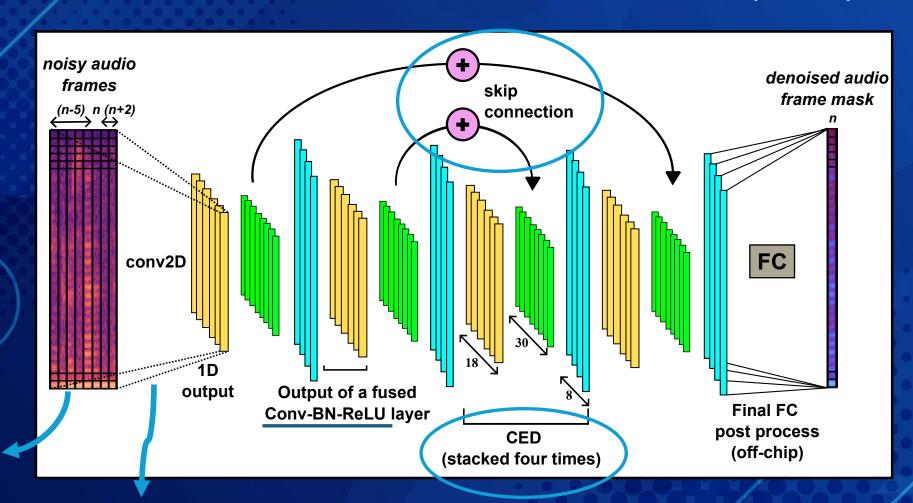

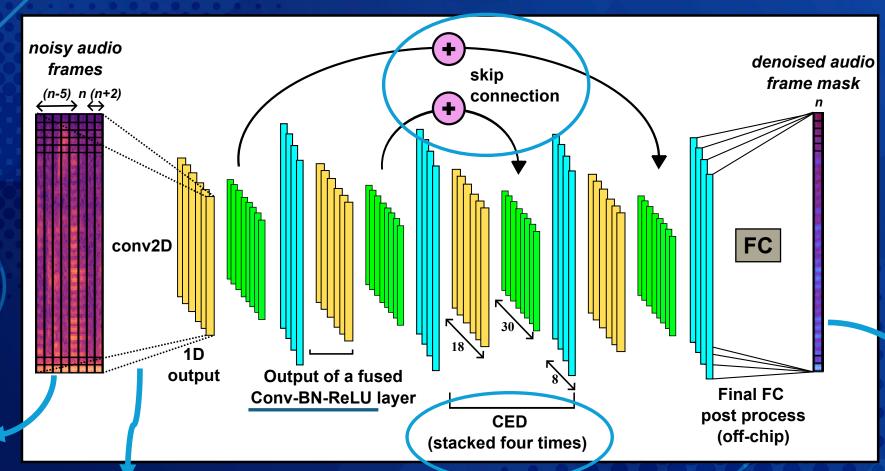

Neural Network: Cascaded Redundant Convolutional Encoder-Decoder (CR-CED)

Neural Network: Cascaded Redundant Convolutional Encoder-Decoder (CR-CED)

Neural Network: Cascaded Redundant Convolutional Encoder-Decoder (CR-CED)

Treated as 2D image

Neural Network: Cascaded Redundant Convolutional Encoder-Decoder (CR-CED)

Treated as 2D image

Single 2D conv

Neural Network: Cascaded Redundant Convolutional Encoder-Decoder (CR-CED)

Treated as 2D image

Single 2D conv

Neural Network: Cascaded Redundant Convolutional Encoder-Decoder (CR-CED)

Treated as 2D image

Single 2D conv

Neural Network: Cascaded Redundant Convolutional Encoder-Decoder (CR-CED)

Treated as 2D image

Single 2D conv

Neural Network: Cascaded Redundant Convolutional Encoder-Decoder (CR-CED)

Treated as 2D image

Single 2D conv

Mask vector: multiplied by the noisy frame to obtain the denoised audio STFT

# Outline

- Introduction

- Design Features

- Algorithm Design

- Quantization Scheme

- Top-level Chip Architecture

- 1D Convolution Dataflow

- Results

- Conclusion

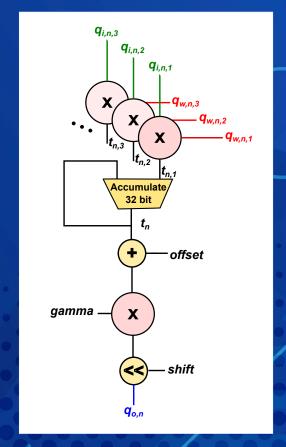

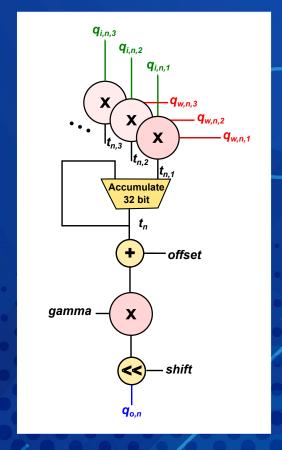

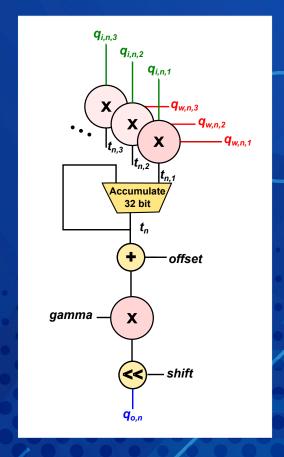

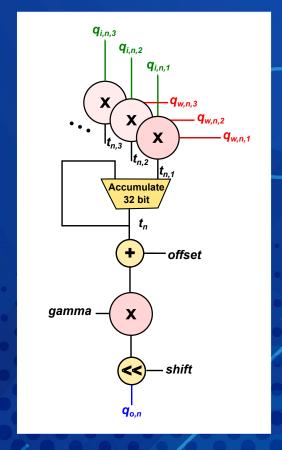

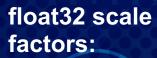

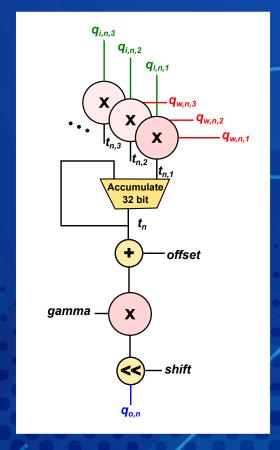

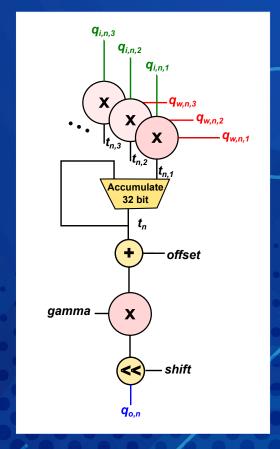

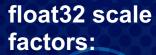

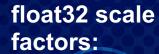

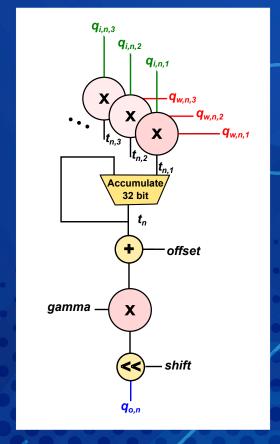

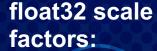

8-bit weight, activation quantization

8-bit weight, activation quantization

Weight:  $w = s_w * (q_w - z_w); z_w = 0$

Input:  $i = s_i * (q_i - z_i)$

Output:  $o = s_o * (q_o - z_o)$

**Offset:**  $b = s_b * (q_b - z_b); z_b = 0$

8-bit weight, activation quantization

Weight:  $w = s_w * (q_w - z_w); z_w = 0$

Input:  $i = s_i * (q_i - z_i)$

Output:  $o = s_o * (q_o - z_o)$

**Offset:**  $b = s_b * (q_b - z_b); z_b = 0$

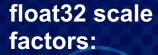

float32 scale factors:

$S_w, S_i, S_o, S_b$

8-bit weight, activation quantization

Weight:  $w = s_w * (q_w - z_w); . z_w = 0$

Input:  $i = s_i * (q_i - z_i)$ Output:  $o = s_o * (q_o - z_o)$

Offset:  $b = s_b * (q_b - z_b); z_b = 0$

$S_w, S_i, S_o, S_b$

8-bit quantized values stored onchip:  $q_w$ ,  $q_i$ ,  $q_o$ ,  $q_b$

8-bit weight, activation quantization

Weight:  $w = s_w * (q_w - z_w); z_w = 0$

Input:  $i = s_i * (q_i - z_i)$

Output:  $o = s_o * (q_o - z_o)$ Offset:  $b = s_b * (q_b - z_b)$ ;  $z_b = 0$

$S_w, S_i, S_o, S_b$

8-bit quantized values stored onchip:  $q_w$ ,  $q_i$ ,  $q_o$ ,  $q_b$  8-bit zero-points:

$\boldsymbol{z}_{w}, \boldsymbol{z}_{i}, \boldsymbol{z}_{o}, \boldsymbol{z}_{b}$

8-bit weight, activation quantization

Weight:  $w = s_w * (q_w - z_w); z_w = 0$

Input:  $i = s_i * (q_i - z_i)$

Output:  $o = s_o * (q_o - z_o)$ Offset:  $b = s_b * (q_b - z_b)$ ;  $z_b = 0$

float32 scale factors:

$S_w, S_i, S_o, S_b$

8-bit quantized values stored onchip:  $q_w$ ,  $q_i$ ,  $q_o$ ,  $q_b$

8-bit zero-points:

$\boldsymbol{z}_{w}, \boldsymbol{z}_{i}, \boldsymbol{z}_{o}, \boldsymbol{z}_{b}$

$$o_n = \sum w_{n,k} * i_{n,k} + b_n$$

8-bit weight, activation quantization

Input:

$$i = s_i * (q_i - z_i)$$

Output:

$$o = s_o * (q_o - z_o)$$

Offset:  $b = s_b * (q_b - z_b)$ ;  $z_b = 0$

$$S_w, S_i, S_o, S_b$$

8-bit quantized values stored onchip:  $q_w$ ,  $q_i$ ,  $q_o$ ,  $q_b$

$$\mathbf{z}_w, \mathbf{z}_i, \mathbf{z}_o, \mathbf{z}_b$$

$$o_n = \sum w_{n,k} * i_{n,k} + b_n$$

8-bit weight, activation quantization

Input:

$$i = s_i * (q_i - z_i)$$

Output:

$$o = s_o * (q_o - z_o)$$

Offset:  $b = s_b * (q_b - z_b)$ ;  $z_b = 0$

$S_w, S_i, S_o, S_b$

8-bit quantized values stored onchip:  $q_w$ ,  $q_i$ ,  $q_o$ ,  $q_b$

$$\boldsymbol{z}_{w}, \boldsymbol{z}_{i}, \boldsymbol{z}_{o}, \boldsymbol{z}_{b}$$

$$o_n = \sum w_{n,k} * i_{n,k} + b_n$$

$$s_{o,n} * (q_{o,n} - z_{o,n}) = \sum [s_{w,n} * q_{w,n,k} * s_{i,n} * (q_{i,n,k} - z_{i,n})] + s_{b,n} * q_{b,n}$$

8-bit weight, activation quantization

$$w = s_w * (q_w - z_w); z_w = 0$$

Input:

$$i = s_i * (q_i - z_i)$$

$$= s_i * (q_i - z_i)$$

$= s_i * (q_i - z_i)$

$$o = s_o * (q_o - z_o)$$

Output:

$$b = s_b * ($$

$$b = s_b * (q_b - z_b); z_b = 0$$

$$S_w, S_i, S_o, S_b$$

8-bit quantized values stored on-

chip:  $q_w$ ,  $q_i$ ,  $q_o$ ,  $q_b$

$$\boldsymbol{z}_{w}, \boldsymbol{z}_{i}, \boldsymbol{z}_{o}, \boldsymbol{z}_{b}$$

$$o_n = \sum w_{n,k} * i_{n,k} + b_n$$

$$s_{o,n} * (q_{o,n} - z_{o,n}) = \sum [s_{w,n} * q_{w,n,k} * s_{i,n} * (q_{i,n,k} - z_{i,n})] + s_{b,n} * q_{b,n}$$

$$q_{o,n} = \left[gamma_n * \left(\sum q_{w,n,k} * q_{i,n,k} + offset_n\right)\right] \gg shift_n$$

Where,

$$gamma_{n} \gg shift_{n} = s_{w,n} * s_{i,n} * s_{o,n}^{-1}$$

$offset_{n} = (z_{o,n}s_{o,n} + s_{b,n}q_{b,n})s_{w,n}^{-1}s_{i,n}^{-1} - z_{i,n}\Sigma q_{w,n,k}$

8-bit weight, activation quantization

**Output:**

Offset:

$$w = s_w * (q_w - z_w); z_w = 0$$

Input:

$$i = s_i * (q_i - z_i)$$

$$= s_i * (q_i - z_i)$$

$$= s_i * (q_i - z_i)$$

$$= s_o * (q_o - z_o)$$

$$o = s_o * (q_o - z_o)$$

$$b = s_o * (q_o - z_o)$$

$$= s_b * (q_b)$$

$$b=s_b*(q_b-z_b); z_b=0$$

$$s_w, s_i, s_o, s_b$$

8-bit quantized values stored on-

chip:  $q_w$ ,  $q_i$ ,  $q_o$ ,  $q_b$

$$\mathbf{Z}_{w}, \mathbf{Z}_{i}, \mathbf{Z}_{o}, \mathbf{Z}_{b}$$

$$o_n = \sum w_{n,k} * i_{n,k} + b_n$$

$$s_{o,n} * (q_{o,n} - z_{o,n}) = \sum \left[ s_{w,n} * q_{w,n,k} * s_{i,n} * (q_{i,n,k} - z_{i,n}) \right] + s_{b,n} * q_{b,n}$$

$$q_{o,n} = \left[ gamma_n * \left( \sum_{q_{w,n,k}} q_{i,n,k} + offset_n \right) \right] \gg shift_n$$

Where,

$$gamma_{n} \gg shift_{n} = s_{w,n} * s_{i,n} * s_{o,n}^{-1}$$

$offset_{n} = (z_{o,n}s_{o,n} + s_{b,n}q_{b,n})s_{w,n}^{-1}s_{i,n}^{-1} - z_{i,n}\Sigma q_{w,n,k}$

8-bit weight, activation quantization

Input:  $i = s_i * (q_i - z_i)$ Output:  $o = s_o * (q_o - z_o)$

Offset:  $b = s_b * (q_b - z_b); z_b = 0$

$S_w, S_i, S_o, S_b$

8-bit quantized values stored onchip:  $q_w$ ,  $q_i$ ,  $q_o$ ,  $q_b$

8-bit zero-points:

$$\boldsymbol{z}_{w}, \boldsymbol{z}_{i}, \boldsymbol{z}_{o}, \boldsymbol{z}_{b}$$

$$o_n = \sum w_{n,k} * i_{n,k} + b_n$$

$$s_{o,n} * (q_{o,n} - z_{o,n}) = \sum [s_{w,n} * q_{w,n,k} * s_{i,n} * (q_{i,n,k} - z_{i,n})] + s_{b,n} * q_{b,n}$$

$$q_{o,n} = ig[ gamma_n * ig( \Sigma ig[ q_{w,n,k} * q_{i,n,k} ig] + offset_n ig) ig] \gg shift_n$$

Where,

$$gamma_{n} \gg shift_{n} = s_{w,n} * s_{i,n} * s_{o,n}^{-1}$$

$offset_{n} = (z_{o,n}s_{o,n} + s_{b,n}q_{b,n})s_{w,n}^{-1}s_{i,n}^{-1} - z_{i,n}\Sigma q_{w,n,k}$

Minimal drop in performance 2.83 to 2.79 PESQ

in the audio quality evaluation score

Skip Connections, Per-kernel Adaptive Rounding

Skip Connections, Per-kernel Adaptive Rounding

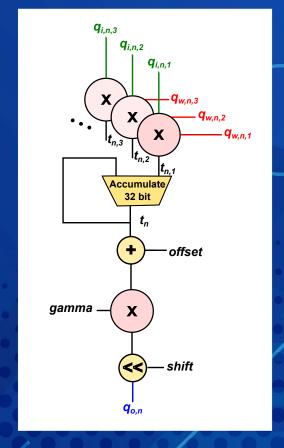

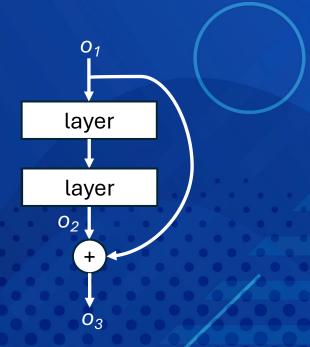

#### **Skip connection computation:**

$$o_3 = o_1 + o_2$$

$s_3(q_{o,3} - z_3) = s_1(q_{o,1} - z_1) + s_2(q_{o,2} - z_2)$

Skip Connections, Per-kernel Adaptive Rounding

#### Skip connection computation:

$$o_3 = o_1 + o_2$$

$s_3(q_{o,3} - z_3) = s_1(q_{o,1} - z_1) + s_2(q_{o,2} - z_2)$

$$q_{o,3} = (s_{skip,1}q_{o,1} + s_{skip,2}q_{o,2} + offset_{skip}) \gg shift_{skip}$$

Skip Connections, Per-kernel Adaptive Rounding

#### Skip connection computation:

$$egin{aligned} o_3 &= o_1 + o_2 \ s_3 ig( q_{o,3} - z_3 ig) &= s_1 ig( q_{o,1} - z_1 ig) + s_2 ig( q_{o,2} - z_2 ig) \end{aligned}$$

$$q_{o,3} = (s_{skip,1}q_{o,1} + s_{skip,2}q_{o,2} + offset_{skip}) \gg shift_{skip}$$

Where,

$$s_{skip,i} \gg shift_{skip} = rac{s_i}{s_3}, \quad i = 1, 2$$

$offset_{skip} \gg shift_{skip} = z_3 - \left(rac{s_1}{s_3}

ight)z_1 - \left(rac{s_2}{s_3}

ight)z_2$

Skip Connections, Per-kernel Adaptive Rounding

#### **Skip connection computation:**

$$o_3 = o_1 + o_2$$

$s_3(q_{o,3} - z_3) = s_1(q_{o,1} - z_1) + s_2(q_{o,2} - z_2)$

$$q_{o,3} = (s_{skip,1}q_{o,1} + s_{skip,2}q_{o,2} + offset_{skip}) \gg shift_{skip}$$

Where,

$$s_{skip,i} \gg shift_{skip} = rac{s_i}{s_3}, \quad i = 1, 2$$

$offset_{skip} \gg shift_{skip} = z_3 - \left(rac{s_1}{s_3}

ight)z_1 - \left(rac{s_2}{s_3}

ight)z_2$

Per-kernel adaptive rounding: Determines how to round and at which precision Adding a constant to  $offset_n$  while eliminating the need for a comparator

# Outline

- Introduction

- Design Features

- Algorithm Design

- Quantization Scheme

- Top-level Chip Architecture

- 1D Convolution Dataflow

- Results

- Conclusion

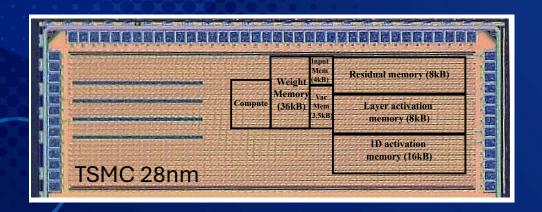

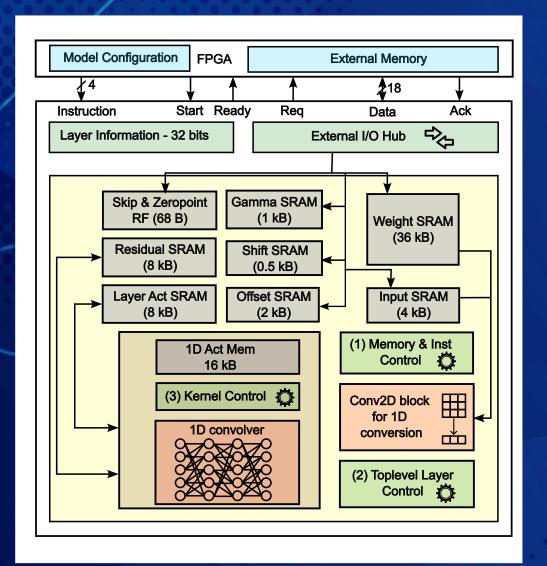

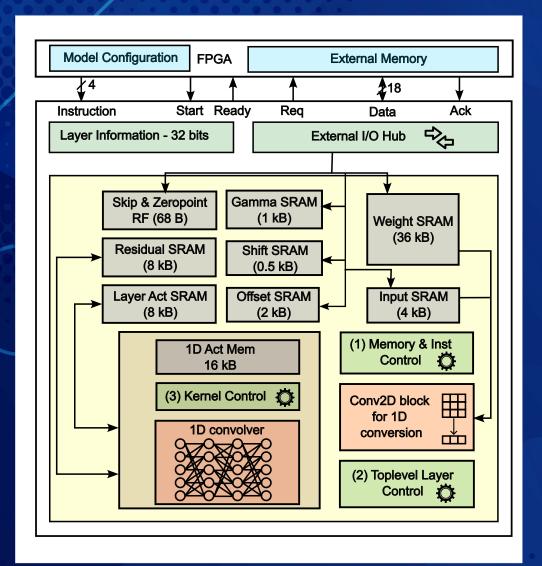

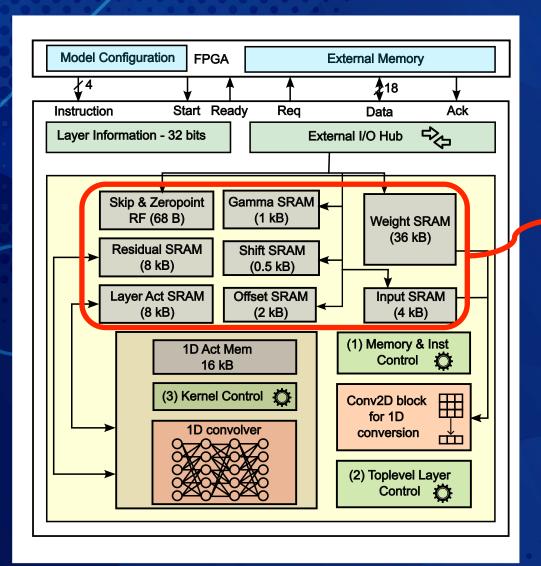

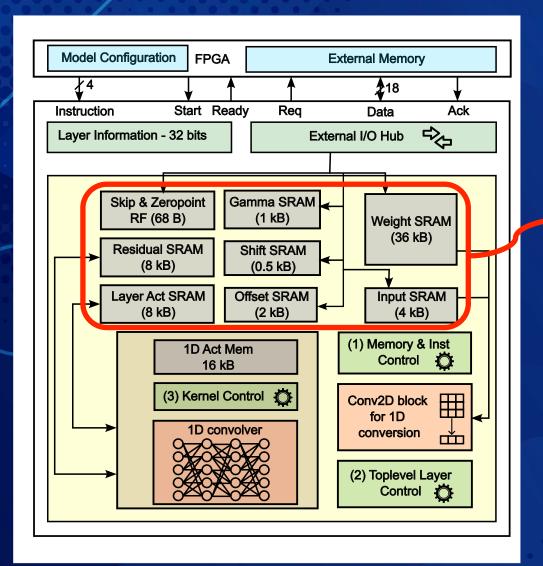

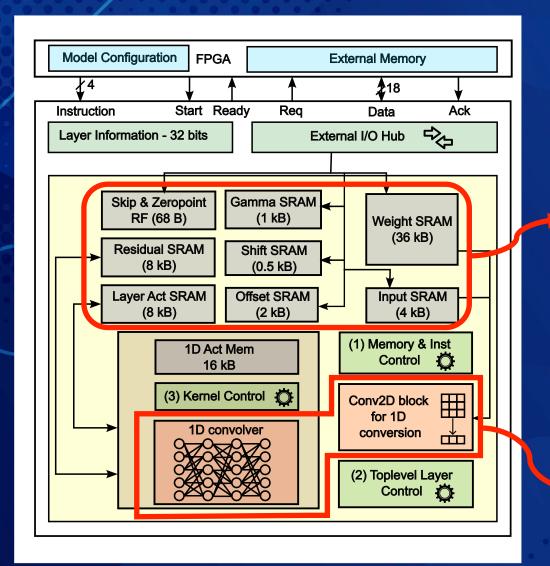

ULSI) Solution Control System

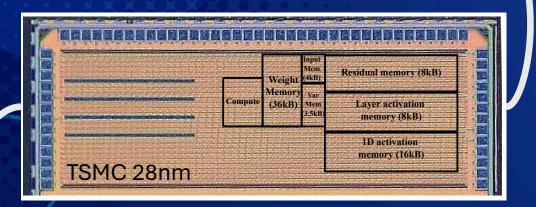

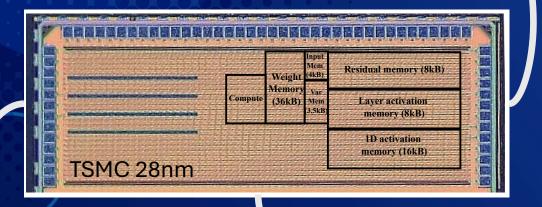

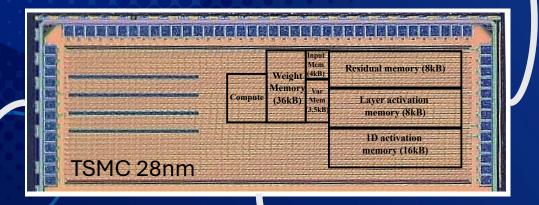

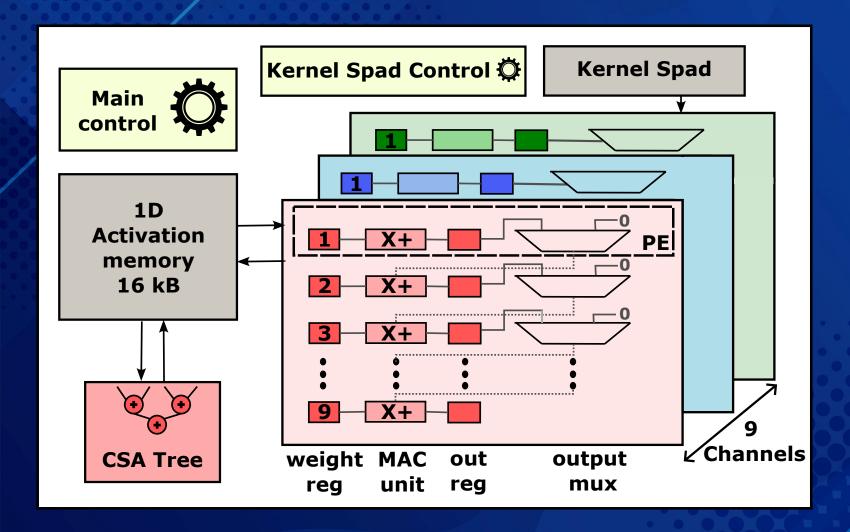

- Reconfigurable Chip Architecture:

- Dynamic configuration for 2D/1D convolution operations, tailored to input and kernel requirements.

- Reconfigurable Chip Architecture:

- Dynamic configuration for 2D/1D convolution operations, tailored to input and kernel requirements.

- On-Chip Data Loading:

- All weights and quantization parameters preloaded, minimizing external data transfers to reduce latency and power.

- Reconfigurable Chip Architecture:

- Dynamic configuration for 2D/1D convolution operations, tailored to input and kernel requirements.

- On-Chip Data Loading:

- All weights and quantization parameters preloaded, minimizing external data transfers to reduce latency and power.

- Optimized Precision and Power:

- Activations stored in 8-bit precision.

- Power-gated memory logic reduces power during inactivity.

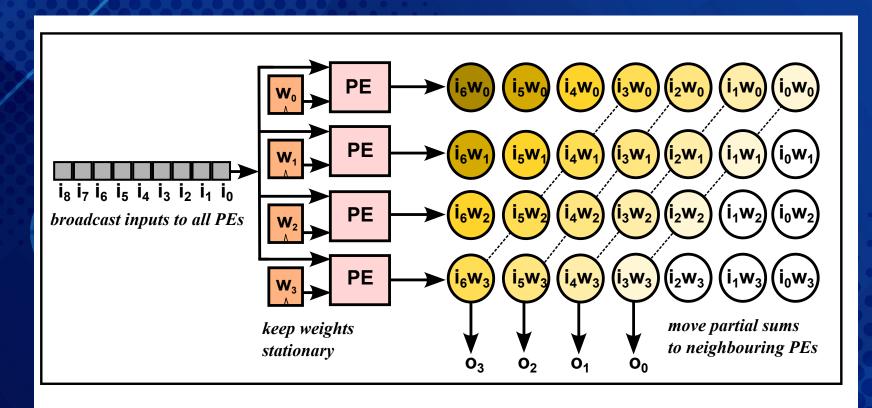

- Reconfigurable Chip Architecture:

- Dynamic configuration for 2D/1D convolution operations, tailored to input and kernel requirements.

- On-Chip Data Loading:

- All weights and quantization parameters preloaded, minimizing external data transfers to reduce latency and power.

- Optimized Precision and Power:

- Activations stored in 8-bit precision.

- Power-gated memory logic reduces power during inactivity.

- Efficient Data Processing:

- Conv2D block reduces 2D to 1D; 1D convolver completes operations with residual memory for skip connections.

# Outline

- Introduction

- Design Features

- Algorithm Design

- Quantization Scheme

- Top-level Chip Architecture

- 1D Convolution Dataflow

- Results

- Conclusion

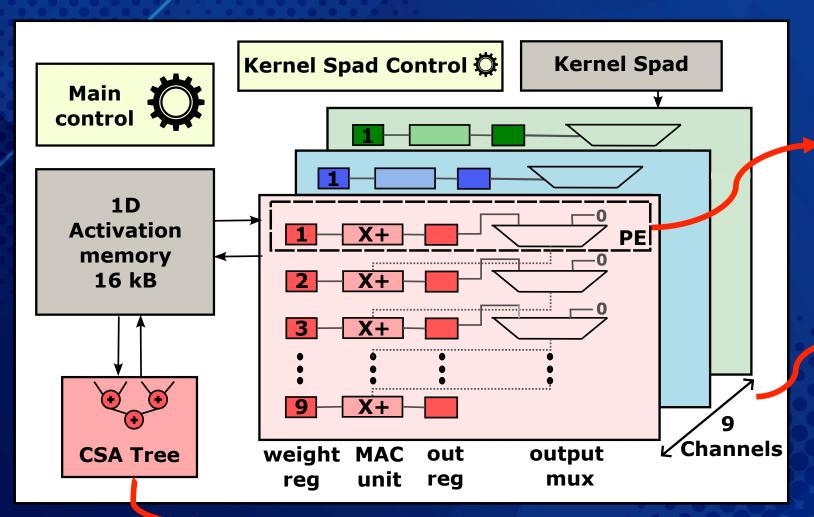

# 1D Convolution Dataflow

Architecture

### 1D Convolution Dataflow

**Architecture**

Processes one kernel at a time with PE

Enables synchronous computation of up to 9 channels

Carry-Save Adder Tree

#### 1D Convolution Dataflow

PE Activation Routing Dataflow

- Energy Optimization via Memory Access Reduction; PE input routing and weight mapping schemes

- Final PE computes a complete kernel convolution output every cycle

# Outline

- Introduction

- Design Features

- Algorithm Design

- Quantization Scheme

- Top-level Chip Architecture

- 1D Convolution Dataflow

- Results

- Conclusion

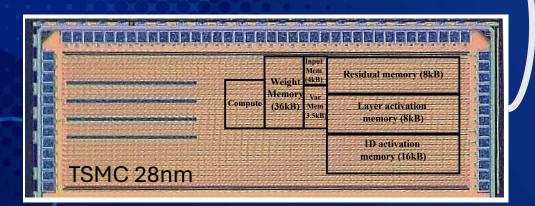

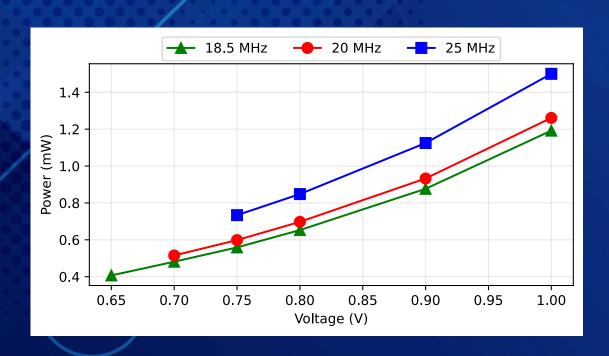

| Technology     | TSMC 28nm HPC+           |

|----------------|--------------------------|

| Core area      | 0.75 mm <sup>2</sup>     |

| On-chip SRAM   | 75.5kB                   |

| Supply voltage | 0.65 – 1V                |

| Frequency      | 18.5MHz                  |

| Power          | 407μW (@ 0.65V, 18.5MHz) |

| Efficiency     | 3.24µJ/frame             |

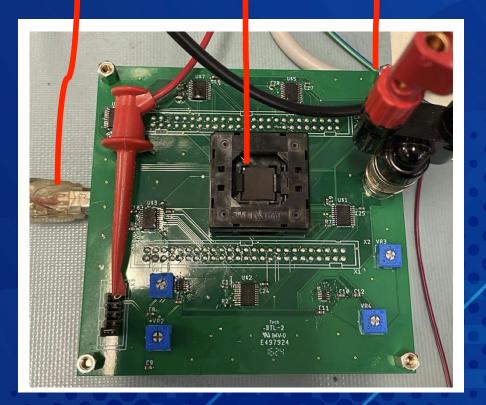

FPGA

XEM7001 Packaged Measurement

(below) Die PCB

Measured voltage scalability of this work

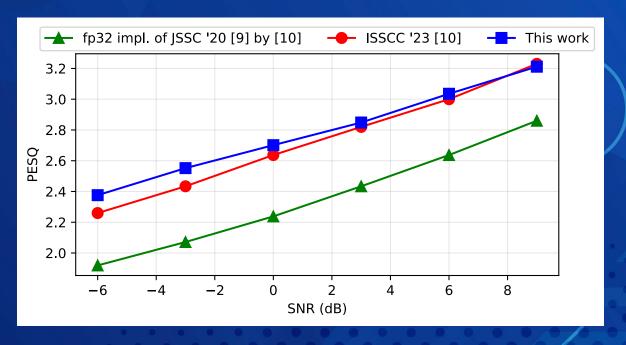

PESQ comparison with prior works

• [9] – CNN based FPGA design [10] - 1D depthwise-separable convolution layers, a gated recurrent unit based ASIC

|                          | TCAS-II'21 [7]        | INTERSPEECH'20 [8] |           | JSSC'20 [9]          | ISSCC'23 [10]                                                 | This Work                     |

|--------------------------|-----------------------|--------------------|-----------|----------------------|---------------------------------------------------------------|-------------------------------|

| Implementation           | Synthesized<br>ASIC   | FPGA               | FPGA      | ASIC                 | ASIC                                                          | ASIC                          |

| Technology (nm)          | 90                    | -                  | -         | 40                   | 28                                                            | 28                            |

| Core Area (mm²)          | 11.4                  | -                  | -         | 4.2                  | 0.81                                                          | 0.75                          |

| FFT Window /<br>Hop      | 512/-                 | 512 / 256          | 400 / 100 | 256 / 128            | 512 / 256                                                     | 256 / 64                      |

| Frequency (MHz)          | 500                   | -                  | -         | 5 - 20               | 2.5 - 20                                                      | 18.5 – 25                     |

| On-Chip SRAM<br>(kB)     |                       | 313.7              | 434.67    | 327                  | 35                                                            | 75.5                          |

| Power (mW)               | 636<br>(1.2V, 500MHz) | 272                | 147.2     | 2.17<br>(0.6V, 5MHz) | 0.74<br>(0.8V, 2.5MHz);<br>1.365<br>(1V, 2.5MHZ) <sup>b</sup> | 0.407ª<br>(0.65V,<br>18.5MHz) |

| Frames/sec               | -                     | 63                 | 160       | 125                  | 63                                                            | 125                           |

| Efficiency<br>(µJ/frame) | 10095.24°             | 4317.46            | 920       | 17.36                | 11.75                                                         | 3.24ª                         |

| Dataset                  | TIMIT                 | CHiME2             | CHiME2    | CHiME2               | CHiME2                                                        | CHiME2                        |

| PESQ                     | 1.52                  | -                  | -         | 2.38 <sup>d</sup>    | 2.73                                                          | 2.79                          |

<sup>&</sup>lt;sup>a</sup>excludes off-chip processing and STFT

<sup>&</sup>lt;sup>b</sup>ML processing power from place-and-route netlist (excludes preprocessing: I/O Buffer, FFT, Window, Mel filter)

<sup>&</sup>lt;sup>c</sup>As per [9], assuming hop size = 50% of FFT window size

<sup>d</sup>fp32 implementation of [8] by [9]

|                          | TCAS-II'21 [7]        | INTERSPEECH'20 [8] |           | JSSC'20 [9]          | ISSCC'23 [10]                                                 | This Work                     |

|--------------------------|-----------------------|--------------------|-----------|----------------------|---------------------------------------------------------------|-------------------------------|

| Implementation           | Synthesized<br>ASIC   | FPGA               | FPGA      | ASIC                 | ASIC                                                          | ASIC                          |

| Technology (nm)          | 90                    | -                  | -         | 40                   | 28                                                            | 28                            |

| Core Area (mm²)          | 11.4                  | -                  | -         | 4.2                  | 0.81                                                          | 0.75                          |

| FFT Window /<br>Hop      | 512/-                 | 512 / 256          | 400 / 100 | 256 / 128            | 512 / 256                                                     | 256 / 64                      |

| Frequency (MHz)          | 500                   | -                  | -         | 5 - 20               | 2.5 - 20                                                      | 18.5 – 25                     |

| On-Chip SRAM<br>(kB)     |                       | 313.7              | 434.67    | 327                  | 35                                                            | 75.5                          |

| Power (mW)               | 636<br>(1.2V, 500MHz) | 272                | 147.2     | 2.17<br>(0.6V, 5MHz) | 0.74<br>(0.8V, 2.5MHz);<br>1.365<br>(1V, 2.5MHZ) <sup>b</sup> | 0.407ª<br>(0.65V,<br>18.5MHz) |

| Frames/sec               | -                     | 63                 | 160       | 125                  | 63                                                            | 125                           |

| Efficiency<br>(µJ/frame) | 10095.24°             | 4317.46            | 920       | 17.36                | 11.75                                                         | 3.24ª                         |

| Dataset                  | TIMIT                 | CHiME2             | CHiME2    | CHiME2               | CHiME2                                                        | CHIME2                        |

| PESQ                     | 1.52                  | -                  | -         | 2.38 <sup>d</sup>    | 2.73                                                          | 2.79                          |

<sup>&</sup>lt;sup>a</sup>excludes off-chip processing and STFT

<sup>&</sup>lt;sup>b</sup>ML processing power from place-and-route netlist (excludes preprocessing: I/O Buffer, FFT, Window, Mel filter)

$<sup>^{\</sup>circ}$ As per [9], assuming hop size = 50% of FFT window size  $^{\circ}$ dfp32 implementation of [8] by [9]

|                          | TCAS-II'21 [7]        | INTERSPEECH'20 [8] |           | JSSC'20 [9]          | ISSCC'23 [10]                                                 | This Work                     |

|--------------------------|-----------------------|--------------------|-----------|----------------------|---------------------------------------------------------------|-------------------------------|

| Implementation           | Synthesized<br>ASIC   | FPGA               | FPGA      | ASIC                 | ASIC                                                          | ASIC                          |

| Technology (nm)          | 90                    | -                  | -         | 40                   | 28                                                            | 28                            |

| Core Area (mm²)          | 11.4                  | -                  | -         | 4.2                  | 0.81                                                          | 0.75                          |

| FFT Window /<br>Hop      | 512/-                 | 512 / 256          | 400 / 100 | 256 / 128            | 512 / 256                                                     | 256 / 64                      |

| Frequency (MHz)          | 500                   | -                  | -         | 5 - 20               | 2.5 - 20                                                      | 18.5 – 25                     |

| On-Chip SRAM<br>(kB)     |                       | 313.7              | 434.67    | 327                  | 35                                                            | 75.5                          |

| Power (mW)               | 636<br>(1.2V, 500MHz) | 272                | 147.2     | 2.17<br>(0.6V, 5MHz) | 0.74<br>(0.8V, 2.5MHz);<br>1.365<br>(1V, 2.5MHZ) <sup>b</sup> | 0.407ª<br>(0.65V,<br>18.5MHz) |

| Frames/sec               | -                     | 63                 | 160       | 125                  | 63                                                            | 125                           |

| Efficiency<br>(µJ/frame) | 10095.24°             | 4317.46            | 920       | 17.36                | 11.75                                                         | 3.24ª                         |

| Dataset                  | TIMIT                 | CHiME2             | CHiME2    | CHiME2               | CHiME2                                                        | CHiME2                        |

| PESQ                     | 1.52                  | -                  | -         | 2.38 <sup>d</sup>    | 2.73                                                          | 2.79                          |

<sup>&</sup>lt;sup>a</sup>excludes off-chip processing and STFT

<sup>&</sup>lt;sup>b</sup>ML processing power from place-and-route netlist (excludes preprocessing: I/O Buffer, FFT, Window, Mel filter)

<sup>&</sup>lt;sup>c</sup>As per [9], assuming hop size = 50% of FFT window size dfp32 implementation of [8] by [9]

|                          | TCAS-II'21 [7]        | INTERSPEECH'20 [8] |           | JSSC'20 [9]          | ISSCC'23 [10]                                                 | This Work                     |

|--------------------------|-----------------------|--------------------|-----------|----------------------|---------------------------------------------------------------|-------------------------------|

| Implementation           | Synthesized<br>ASIC   | FPGA               | FPGA      | ASIC                 | ASIC                                                          | ASIC                          |

| Technology (nm)          | 90                    | -                  | -         | 40                   | 28                                                            | 28                            |

| Core Area (mm²)          | 11.4                  | -                  | -         | 4.2                  | 0.81                                                          | 0.75                          |

| FFT Window /<br>Hop      | 512/-                 | 512 / 256          | 400 / 100 | 256 / 128            | 512 / 256                                                     | 256 / 64                      |

| Frequency (MHz)          | 500                   | -                  | -         | 5 - 20               | 2.5 - 20                                                      | 18.5 – 25                     |

| On-Chip SRAM<br>(kB)     |                       | 313.7              | 434.67    | 327                  | 35                                                            | 75.5                          |

| Power (mW)               | 636<br>(1.2V, 500MHz) | 272                | 147.2     | 2.17<br>(0.6V, 5MHz) | 0.74<br>(0.8V, 2.5MHz);<br>1.365<br>(1V, 2.5MHZ) <sup>b</sup> | 0.407ª<br>(0.65V,<br>18.5MHz) |

| Frames/sec               | -                     | 63                 | 160       | 125                  | 63                                                            | 125                           |

| Efficiency<br>(µJ/frame) | 10095.24°             | 4317.46            | 920       | 17.36                | 11.75                                                         | 3.24ª                         |

| Dataset                  | TIMIT                 | CHiME2             | CHiME2    | CHiME2               | CHiME2                                                        | CHIME2                        |

| PESQ                     | 1.52                  | -                  | -         | 2.38 <sup>d</sup>    | 2.73                                                          | 2.79                          |

<sup>&</sup>lt;sup>a</sup>excludes off-chip processing and STFT

<sup>&</sup>lt;sup>b</sup>ML processing power from place-and-route netlist (excludes preprocessing: I/O Buffer, FFT, Window, Mel filter)

<sup>&</sup>lt;sup>c</sup>As per [9], assuming hop size = 50% of FFT window size

<sup>d</sup>fp32 implementation of [8] by [9]

|                          | TCAS-II'21 [7]        | INTERSPEECH'20 [8] |           | JSSC'20 [9]          | ISSCC'23 [10]                                                 | This Work                     |

|--------------------------|-----------------------|--------------------|-----------|----------------------|---------------------------------------------------------------|-------------------------------|

| Implementation           | Synthesized<br>ASIC   | FPGA               | FPGA      | ASIC                 | ASIC                                                          | ASIC                          |

| Technology (nm)          | 90                    | -                  | -         | 40                   | 28                                                            | 28                            |

| Core Area (mm²)          | 11.4                  | -                  | -         | 4.2                  | 0.81                                                          | 0.75                          |

| FFT Window /<br>Hop      | 512/-                 | 512 / 256          | 400 / 100 | 256 / 128            | 512 / 256                                                     | 256 / 64                      |

| Frequency (MHz)          | 500                   | -                  | -         | 5 - 20               | 2.5 - 20                                                      | 18.5 – 25                     |

| On-Chip SRAM<br>(kB)     |                       | 313.7              | 434.67    | 327                  | 35                                                            | 75.5                          |

| Power (mW)               | 636<br>(1.2V, 500MHz) | 272                | 147.2     | 2.17<br>(0.6V, 5MHz) | 0.74<br>(0.8V, 2.5MHz);<br>1.365<br>(1V, 2.5MHZ) <sup>b</sup> | 0.407ª<br>(0.65V,<br>18.5MHz) |

| Frames/sec               | -                     | 63                 | 160       | 125                  | 63                                                            | 125                           |

| Efficiency<br>(µJ/frame) | 10095.24°             | 4317.46            | 920       | 17.36                | 11.75                                                         | 3.24ª                         |

| Dataset                  | TIMIT                 | CHiME2             | CHiME2    | CHiME2               | CHiME2                                                        | CHiME2                        |

| PESQ                     | 1.52                  | -                  | -         | 2.38 <sup>d</sup>    | 2.73                                                          | 2.79                          |

<sup>&</sup>lt;sup>a</sup>excludes off-chip processing and STFT

<sup>&</sup>lt;sup>b</sup>ML processing power from place-and-route netlist (excludes preprocessing: I/O Buffer, FFT, Window, Mel filter)

<sup>&</sup>lt;sup>c</sup>As per [9], assuming hop size = 50% of FFT window size dfp32 implementation of [8] by [9]

# Outline

- Introduction

- Design Features

- Algorithm Design

- Quantization Scheme

- Top-level Chip Architecture

- 1D Convolution Dataflow

- Results

- Conclusion

- Quantized convolutional encoder-decoder model tailored for wearable IoT devices and hearing aids

- Hardware quantization to reduce memory and computational demands

- Quantized convolutional encoder-decoder model tailored for wearable IoT devices and hearing aids

- Hardware quantization to reduce memory and computational demands

- Low power (407μW), or 3.24μJ per frame at 0.65V and 18.5 MHz

- High audio quality (PESQ: highest among prior works)

- Real-time processing: < 8ms per frame at 18.5 MHz</li>

- Quantized convolutional encoder-decoder model tailored for wearable IoT devices and hearing aids

- Hardware quantization to reduce memory and computational demands

- Low power (407μW), or 3.24μJ per frame at 0.65V and 18.5 MHz

- High audio quality (PESQ: highest among prior works)

- Real-time processing: < 8ms per frame at 18.5 MHz</li>

- Future Work:

- Integration of frequency transform computation with on-chip processor

- Development of a complete system (including ADC and DAC)

# Acknowledgment

- We would like to thank MIT-IBM Watson AI Lab for funding.

- We would also like to thank the TSMC University Shuttle Program for tapeout support.

- We would also like to thank Zexi Ji for the communication interface code.

# Thank you!